| 2パターンテストを可能にした半導体集積回路 |

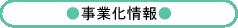

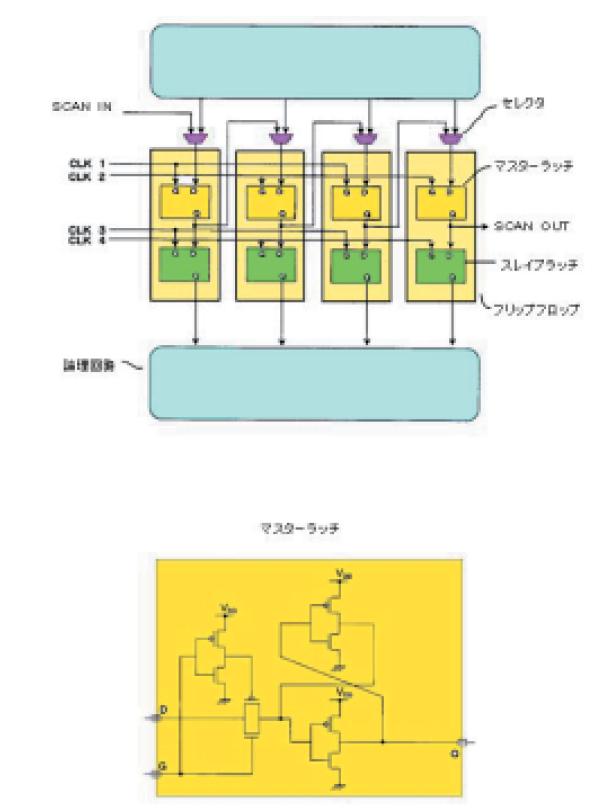

| 本発明は大幅な占有面積の増加をもたらすことなく、2パターンテストが可能になる半導体集積回路を提供するものである。その特徴は、複数のフリップフロップと各フリップフロップに対応して設けられた複数のセレクタを有し、各フリップフロップはマスターラッチとマスターラッチの出力端子Qにその入力端子Dが接続されたスレーブラッチを有し、各セレクタの出力端子は対応するフリップフロップのマスターラッチの入力端子Dに接続し、マスターラッチの出力端子Qは隣接するセレクタの入力端子に接続し、これによって入力端子SCAN INから入力されたスキャンテスト信号が第1のフリップフロップのマスターラッチ、第2のフリップフロップのマスターラッチ、第3のフリップフロップのマスターラッチ、第4のフリップフロップのマスターラッチの順にスレーブラッチを介すことなく順次付与される回路構成を実現した点にある。この構成により、2パターンテストのためのスキャンテスト信号、即ち連続して入力した1パターン目のテストパターンと2パターン目のテストパターンが、出力端子SCAN OUTから連続して出力でき、2パターンテストが可能となる。 |

| ユーザー業界 | 活 用 ア イ デ ア |

電気・電子 | 集積回路の製造 ○集積回路を開発・設計・製造・販売する 集積回路のテスト ○集積回路のテストをのみを専門にする 集積回路のテスト機器の製造 ○集積回路のテストに使用する機器を製造・販売する |

| 関連特許 | なし |

| 特許情報 |

・実施段階:実施無し ・技術導入時の技術指導の有無:応相談 ・ノウハウ提供:応相談 ・ライセンス制約条件について:許諾のみ |

| market potential | 特許請求の範囲は半導体集積回路となっていて、2パターンテストに適した回路構成の半導体集積回路を規定しており、テスト段階で2パターンテストを実施したか否かに拘わらず回路構成を検証することにより特許侵害の有無が判断できるようになっている。また、本発明は半導体集積回路のテストを専門に行うことを業とする分野、半導体集積回路用テスト装置を製造・販売・レンタルを業とする分野においても利用が期待される。経済産業省の機械統計確報によれば、集積回路の市場規模は3兆円程度であり、本発明が貢献する市場は極めて大きい。更に、本発明の2パターンテストを実現する回路構成は、半導体集積回路以外においても利用でき、例えばプリント基板上に電子部品を搭載して電子回路を構成したモジュール、CPUから配線まで全て光信号を扱う部品を用いた光コンピュータにおいても本発明の技術思想が利用できる。 |

|