電子回路および双安定回路

- 開放特許情報番号

- L2024001054

- 開放特許情報登録日

- 2024/5/2

- 最新更新日

- 2025/2/27

基本情報

| 出願番号 | 特願2024-008654 |

|---|---|

| 出願日 | 2020/3/18 |

| 出願人 | 国立研究開発法人科学技術振興機構 |

| 公開番号 | |

| 公開日 | 2024/3/19 |

| 登録番号 | |

| 特許権者 | 国立研究開発法人科学技術振興機構 |

| 発明の名称 | 電子回路および双安定回路 |

| 技術分野 | 情報・通信、電気・電子 |

| 機能 | 機械・部品の製造 |

| 適用製品 | 電子回路および双安定回路に関し、例えば双安定回路およびその双安定回路を有する複数のメモリセルを備えた電子回路 |

| 目的 | 消費電力および消費エネルギーを抑制する。 |

| 効果 | 消費電力および消費エネルギーを抑制することができる。 |

技術概要 |

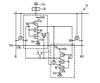

ソースが第1電源線、ドレインが出力、ゲートが入力ノードに接続された第1導電型のチャネルの第1FETと、

ソースが第1電源線との間に電源電圧が供給される第2電源線に接続され、ドレインが中間、ゲートが入力ノードに接続された前記第1導電型と反対の第2導電型のチャネルの第2FETと、 ソースが中間ドレインが出力、ゲートが入力ノードに接続された第2導電型のチャネルの第3FETと、 ソースおよびドレインの一方が前記中間ノードに接続され、他方が制御ノードに接続された前記第1導電型のチャネルの第4FETと、 を各々備える第1インバータ回路および第2インバータ回路と、 第1インバータ回路の出力および第2インバータ回路の入力ノードが接続された第1記憶ノードと、 第1インバータ回路の入力および前記第2インバータ回路の出力ノードが接続された第2記憶ノードと、を備え、 第1インバータ回路の第4FETのゲートは、第1インバータ回路の入力または第2インバータ回路の出力ノードに接続され、 第2インバータ回路の第4FETのゲートは第2インバータ回路の入力または第1インバータ回路の出力ノードに接続された双安定回路。 |

| 実施実績 | 【無】 |

| 許諾実績 | 【無】 |

| 特許権譲渡 | 【否】 |

| 特許権実施許諾 | 【可】 |

登録者情報

| 登録者名称 | |

|---|---|

その他の情報

| 関連特許 |

|

|---|