遅延量測定回路および遅延量測定方法

- 開放特許情報番号

- L2019000819

- 開放特許情報登録日

- 2019/6/12

- 最新更新日

- 2019/6/12

基本情報

| 出願番号 | 特願2014-209085 |

|---|---|

| 出願日 | 2014/10/10 |

| 出願人 | 地方独立行政法人東京都立産業技術研究センター |

| 公開番号 | |

| 公開日 | 2016/5/16 |

| 登録番号 | |

| 特許権者 | 地方独立行政法人東京都立産業技術研究センター |

| 発明の名称 | 遅延量測定回路および遅延量測定方法 |

| 技術分野 | 電気・電子、情報・通信 |

| 機能 | 機械・部品の製造 |

| 適用製品 | 遅延量測定回路および遅延量測定方法 |

| 目的 | 測定することができる遅延量の大小を選択して広範な測定を実現することができ、少ない回路リソースにより、省電力と小回路規模を実現することができる遅延量測定回路および遅延量測定方法の提供。 |

| 効果 | 複数の遅延素子のうちの1つに入力された第一信号が、各遅延素子を巡回する度に遅延すると共に、各遅延素子に接続されたカウンタに、遅延素子の出力がクロック入力として入力され、このクロック入力が入力される度に計数され、この計数がカウンタの上限値に至ってオーバーフローするまで繰り返される。したがって、小さな遅延量から大きな遅延量まで、測定することができる遅延量の大小を選択して広範な測定を実現することができる。 |

技術概要 |

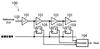

第一信号と第二信号との時間差を測定する遅延量測定回路において、

環状に接続された複数の遅延素子と、 この遅延素子に入力される前記第一信号のうちの一つを選択する入力信号選択回路と、 各前記遅延素子に接続されて前記遅延素子の出力をクロック入力とし、このクロック入力が入力される度に計数するカウンタと、が備えられ、 複数の前記遅延素子のうちの一つに入力された前記第一信号が、各前記遅延素子を巡回する度に遅延すると共に前記カウンタに入力され、 前記遅延素子に入力された前記第二信号に基づいて、前記遅延素子の出力が停止すると共に前記カウンタの計数が停止し、 選択された前記第一信号に基づく前記時間差が測定され、前記入力信号選択回路による選択が繰り返される度に測定された複数の前記時間差から測定結果を算出する演算回路が備えられた、 ことを特徴とする遅延量測定回路。 |

| 実施実績 | 【無】 |

| 許諾実績 | 【無】 |

| 特許権譲渡 | 【否】 |

| 特許権実施許諾 | 【可】 |

登録者情報

| 登録者名称 | |

|---|---|

その他の情報

| 関連特許 |

|

|---|