薄膜トランジスタ、薄膜トランジスタの製造方法および半導体装置

- 開放特許情報番号

- L2018001263

- 開放特許情報登録日

- 2018/6/15

- 最新更新日

- 2018/6/15

基本情報

| 出願番号 | 特願2014-016635 |

|---|---|

| 出願日 | 2014/1/31 |

| 出願人 | 国立研究開発法人物質・材料研究機構 |

| 公開番号 | |

| 公開日 | 2015/8/6 |

| 登録番号 | |

| 特許権者 | 国立研究開発法人物質・材料研究機構 |

| 発明の名称 | 薄膜トランジスタ、薄膜トランジスタの製造方法および半導体装置 |

| 技術分野 | 電気・電子 |

| 機能 | 材料・素材の製造 |

| 適用製品 | 薄膜トランジスタ、薄膜トランジスタの製造方法および半導体装置 |

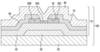

| 目的 | ソース電極およびドレイン電極と半導体層との界面が3次元構造を有することで、ソース電極およびドレイン電極と半導体層との間の界面面積を大きくして、ソース電極およびドレイン電極のレイアウト面積を大きくすることなく、ソース電極およびドレイン電極と半導体層との間のコンタクト抵抗を低減した薄膜トランジスタとその製造方法を提供する。また、このような薄膜トランジスタを有する半導体装置を提供する。 |

| 効果 | ソース電極およびドレイン電極と半導体層との界面が3次元構造を有することで、ソース電極およびドレイン電極と半導体層との間の界面面積を大きくして、ソース電極およびドレイン電極のレイアウト面積を大きくすることなく、ソース電極およびドレイン電極と半導体層との間のコンタクト抵抗を低減した薄膜トランジスタ及びその製造方法を提供することができる。また、このような薄膜トランジスタを有する半導体装置を提供することができる。 |

技術概要 |

ソース電極およびドレイン電極と、

前記ソース電極および前記ドレイン電極に接して設けられた半導体層と、 前記ソース電極および前記ドレイン電極の間のチャネルに対応させて設けられたゲート電極と、 前記ゲート電極と前記半導体層との間に設けられた絶縁体層と、を備え、 前記半導体層が均一の組成であり、 前記ソース電極および前記ドレイン電極のうち少なくとも一方と前記半導体層との界面が3次元構造を有し、 前記チャネルに対応する前記半導体層の少なくとも一部の膜厚が、前記ソース電極および前記ドレイン電極のうちの少なくとも一方との前記界面を有する前記半導体層の少なくとも一部の膜厚と比較して薄い、 薄膜トランジスタ。 |

| 実施実績 | 【無】 |

| 許諾実績 | 【無】 |

| 特許権譲渡 | 【否】 |

| 特許権実施許諾 | 【可】 |

登録者情報

| 登録者名称 | |

|---|---|

その他の情報

| 関連特許 |

|

|---|