再構成可能な遅延回路、並びにその遅延回路を用いた遅延モニタ回路、ばらつき補正回路、ばらつき測定方法及びばらつき補正方法

- 開放特許情報番号

- L2018000320

- 開放特許情報登録日

- 2018/2/15

- 最新更新日

- 2022/8/25

基本情報

| 出願番号 | 特願2015-532785 |

|---|---|

| 出願日 | 2014/7/29 |

| 出願人 | 国立研究開発法人科学技術振興機構 |

| 公開番号 | |

| 公開日 | 2015/2/26 |

| 登録番号 | |

| 特許権者 | 国立研究開発法人科学技術振興機構 |

| 発明の名称 | 再構成可能な遅延回路、並びにその遅延回路を用いた遅延モニタ回路、ばらつき補正回路、ばらつき測定方法及びばらつき補正方法 |

| 技術分野 | 電気・電子、情報・通信 |

| 機能 | 機械・部品の製造 |

| 適用製品 | 遅延モニタ回路及び再構成可能な遅延回路、集積回路におけるトランジスタのばらつきを測定、補正する回路及び方法 |

| 目的 | 集積回路が動作する際の信号伝搬時間をチップ上で測定する遅延モニタ回路に用いられる遅延回路であって、遅延モニタ回路に関するチップ面積の増大を抑制し、製造コストの低減を実現可能な遅延回路を提供する。 |

| 効果 | 本発明の遅延回路はその遅延特性を様々に変化させることができる。このため、測定したい遅延特性に応じて複数の遅延モニタ回路を用意する必要がなく、単一の遅延モニタ回路を用いてトランジスタばらつきの評価を行うことができる。その結果、チップ面積の増大を抑制し、製造コストの低減を実現できる。 |

技術概要 |

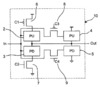

集積回路内の信号伝搬時間の遅延を測定する遅延モニタ回路に含まれる再構成可能な遅延回路であって、

入力信号を入力する入力ノードと、 出力信号を出力する出力ノードと、 入力信号に基づきオンしたときに電源電位を出力ノードに接続するプルアップ回路と、入力信号に基づきオンしたときにグランド電位を出力ノードに接続するプルダウン回路との直列回路を含む第1の反転回路と、 入力信号に基づきオンしたときに電源電位を出力ノードに接続するプルアップ回路と、入力信号に基づきオンしたときにグランド電位を出力ノードに接続するプルダウン回路との直列回路を含む第2の反転回路と、 電源電位と出力ノードの間において、第1の反転回路のプルアップ回路と直列に接続された第1のパストランジスタと、 グランド電位と出力ノードの間において、第1の反転回路のプルダウン回路とに直列に接続された第2のパストランジスタと、 入力ノードと第2の反転回路のプルアップ回路の入力との間に直列に接続された第3のパストランジスタと、 入力ノードと第2の反転回路のプルダウン回路の入力との間に直列に接続された第4のパストランジスタと、を備えることを特徴とする遅延回路。 |

| 実施実績 | 【無】 |

| 許諾実績 | 【無】 |

| 特許権譲渡 | 【否】 |

| 特許権実施許諾 | 【可】 |

登録者情報

| 登録者名称 | |

|---|---|

その他の情報

| 関連特許 |

|

|---|