| 出願番号 |

特願2010-521665 |

| 出願日 |

2009/7/3 |

| 出願人 |

国立研究開発法人科学技術振興機構 |

| 公開番号 |

WO2010/010802 |

| 公開日 |

2010/1/28 |

| 登録番号 |

特許第5168605号 |

| 特許権者 |

国立研究開発法人科学技術振興機構 |

| 発明の名称 |

pチャネル薄膜トランジスタとその製造方法 |

| 技術分野 |

電気・電子、情報・通信、その他 |

| 機能 |

機械・部品の製造、材料・素材の製造、その他 |

| 適用製品 |

薄膜トランジスタ |

| 目的 |

この発明は、酸化第一スズ(SnO)半導体を活性層としたpチャネル薄膜トランジスタとその製造方法を提供する。 |

| 効果 |

この発明によれば、CMOS回路用など実用回路に用いることができるpチャネルで動作する正孔移動度が0.1cm↑2/(Vs)以上の酸化物TFTを提供できるという顕著な効果を奏する。 |

技術概要

|

アモルファスSi又は多結晶Siに代り、酸化物を活性層とする薄膜トランジスタ(TFT)については、近年、酸化亜鉛を活性層とするトランジスタの研究開発がなされている。酸化亜鉛を活性層とするTFTはワイドギャップ半導体を活性層としているため、可視光を透過する透明TFTが作成できる。しかし、酸化亜鉛は電子キャリア濃度が小さく、高温度成膜などの特殊工程が必要になる。これに代わって、SnO↓2薄膜をチャネルとするTFTが報告されているが、これまでのものでは十分な電界移動度のものが得られていない。この発明のSnOを活性層としたpチャネル薄膜トランジスタは、Sn↑4↑+及びSn↑0(錫金属)の含有量が、合計で10原子%未満である酸化第一スズ(SnO)薄膜を薄膜トランジスタの基板上に堆積し、チャネル層としたことを特徴とするpチャネル薄膜トランジスタである。気相法による場合、SnOをターゲットとして用いて、基板上に堆積するSnの酸化度合いを基板温度及び雰囲気酸素分圧により制御して成膜することにより、正孔移動度の高いFETを得ることができる。 |

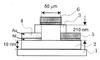

| イメージ図 |

|

| 実施実績 |

【無】 |

| 許諾実績 |

【無】 |

| 特許権譲渡 |

【否】

|

| 特許権実施許諾 |

【可】

|