| 出願番号 |

特願2005-357529 |

| 出願日 |

2005/12/12 |

| 出願人 |

独立行政法人 宇宙航空研究開発機構、HIREC株式会社 |

| 公開番号 |

特開2007-166066 |

| 公開日 |

2007/6/28 |

| 登録番号 |

特許第4332652号 |

| 特許権者 |

国立研究開発法人宇宙航空研究開発機構 |

| 発明の名称 |

シングルイベント耐性のラッチ回路及びフリップフロップ回路 |

| 技術分野 |

電気・電子、情報・通信、その他 |

| 機能 |

機械・部品の製造、制御・ソフトウェア、検査・検出 |

| 適用製品 |

メモリ装置、集積回路、半導体素子 |

| 目的 |

この発明は、シングルイベント現象が発生しにくく、シングルイベントトランジェント(SET)現象が発生しても、その回路への影響を排除することができるラッチ回路及びフリップフロップ回路を提供する。 |

| 効果 |

この発明によれば、ラッチ回路をデュアルポートインバータと、トランスミッションゲートを含まないデュアルポートクロックドインバータとからなる構成としたため、形成される強電界領域が、トランスミッションゲートを含む従来のラッチ回路に比べて狭くなり、シングルイベント現象が発生しにくくなるという効果が得られる。 |

技術概要

|

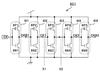

半導体素子で構成されるメモリ回路などにおいて、それらの素子に放射線、イオン線などの高エネルギー粒子が入射されると、素子内に電子―正孔対が発生し、半導体素子が記憶しているデータが反転する、シングルイベントアップセット(SEU)と呼ばれる、誤動作を起こすことがある、このため、従来からシングルイベント耐性を有する回路が用いられていた。しかし、これらの回路では十分な耐性がえられなかった。この発明の回路は、十分なシングルイベント耐性を有するもので、形成される強電界領域を狭くするために、ラッチ回路をデュアルポートインバータと、トランスミッションゲートを含まないデュアルポートクロックドインバータとから構成する。SET現象の影響をクロックに遅延時間を設けることにより排除するが、その遅延時間によってホールド時間が増加させられることを防止するために、一方の記憶ノードへは、その記憶ノード及び全体のラッチモードからスルーモードへの移行が遅延させられるような前縁エッジ遅延クロックが入力される。 |

| イメージ図 |

|

| 実施実績 |

【無】 |

| 許諾実績 |

【有】 |

| 特許権譲渡 |

【否】

|

| 特許権実施許諾 |

【可】

|