半導体集積回路

- 開放特許情報番号

- L2009001672

- 開放特許情報登録日

- 2009/3/14

- 最新更新日

- 2025/3/26

基本情報

| 出願番号 | 特願2006-266835 |

|---|---|

| 出願日 | 2006/9/29 |

| 出願人 | 国立大学法人 千葉大学 |

| 公開番号 | |

| 公開日 | 2008/4/24 |

| 登録番号 | |

| 特許権者 | 国立大学法人 千葉大学 |

| 発明の名称 | 半導体集積回路 |

| 技術分野 | 電気・電子 |

| 機能 | 制御・ソフトウェア |

| 適用製品 | 半導体集積回路 |

| 目的 | 面積の増大及び動作回路の低下を防止することができるエラートレラント方法及びそれを使用可能な半導体集積回路を提供する。 |

| 効果 | 面積の増大及び動作回路の低下を防止可能なエラートレラント方法及びそれを使用可能な半導体集積回路を提供することができる。 |

技術概要 |

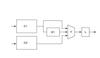

図は、この半導体集積回路の機能ブロックを示す図である。この回路は、第一の組み合わせ回路部C1と、この第一の組み合わせ回路部C1に接続される遅延回路部(遅延時間δ)D1と、第二の組み合わせ回路部C2と、第一の組み合わせ回路部C1、遅延回路部D1及び第二の組み合わせ回路部C2とに接続される多数決回路部Vと、この多数決回路部Vに接続されるラッチ回路部Lと、を有して構成している。第一の組み合わせ回路部C1は、所定の入力を受け付け、一定の結果を出力することができる回路部(論理回路)である。第二の組み合わせ回路部C2は、第一の組み合わせ回路部と同一の機能を実現することができる回路部であり、例えば、第一の組み合わせ回路部C1と第二の組み合わせ回路部C2に同一の値がそれぞれ入力された場合、第一の組み合わせ回路部C1及び第二の組み合わせ回路部C2は同一の結果を出力する。これにより、一方がソフトエラーを発生させた場合であっても、他方はソフトエラーのない正常な値の出力を行うことができていると考えられ、これにより信頼性を高くすることができる。 |

| 実施実績 | 【無】 |

| 許諾実績 | 【無】 |

| 特許権譲渡 | 【否】 |

| 特許権実施許諾 | 【可】 |

登録者情報

| 登録者名称 | |

|---|---|

その他の情報

| 関連特許 |

|

|---|