A/D変換器および読み出し回路

- 開放特許情報番号

- L2009000641

- 開放特許情報登録日

- 2009/2/6

- 最新更新日

- 2011/9/9

基本情報

| 出願番号 | 特願2008-527759 |

|---|---|

| 出願日 | 2007/7/31 |

| 出願人 | 国立大学法人静岡大学 |

| 公開番号 | |

| 公開日 | 2008/2/7 |

| 登録番号 | |

| 特許権者 | 国立大学法人静岡大学 |

| 発明の名称 | A/D変換器および読み出し回路 |

| 技術分野 | 電気・電子 |

| 機能 | 機械・部品の製造 |

| 適用製品 | A/D変換器および読み出し回路 |

| 目的 | CMOSイメージセンサの画素からの信号にノイズキャンセルを施すことが可能なA/D変換器および読み出し回路を提供する。 |

| 効果 | CMOSイメージセンサの画素からの信号にノイズキャンセルを施すことが可能なA/D変換器および読み出し回路が提供できる。 |

技術概要 |

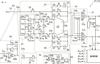

図1はA/D変換器の回路図である。A/D変換器11は、CMOSイメージセンサのために用いられる。図2はCMOSイメージセンサのブロックを示す図面である。A/D変換器11は、CMOSイメージセンサ1において用いられる。CMOSイメージセンサ1では、セルアレイ2はCMOSイメージセンサ画素2aが行方向および列方向に配列されている。画素2aは、リセット状態における第1の信号S1と光誘起信号出力における第2の信号S2とを生成する。A/D変換器11の人力13が画素2aに接続されている。A/D変換器11では、ゲインステージ15の人力15aは、画素2aからの信号を受ける。また、A/D変換器11は、第1の期間T1に第1の信号S1の複数回の標本化と標本値の積分を行うと共に第2の期間T2に第2の信号S2の複数回の標本化と標本値の積分を行う。A/D変換回路17は、第2の期間T2において、ゲインステージ15の出力15bからの信号に応じたディジタル信号を提供し、このディジタル信号は第1および第2の値(例えば、「1」および「O」)を取りうる。図3は、イメージセンサの読み出し回路を示す図面である。 |

| イメージ図 | |

| 実施実績 | 【有】 |

| 許諾実績 | 【有】 |

| 特許権譲渡 | 【否】 |

| 特許権実施許諾 | 【可】 |

登録者情報

| 登録者名称 | |

|---|---|

その他の情報

| 関連特許 |

|

|---|